Motorola 6809

| |

| General information | |

|---|---|

| Launched | 1978 |

| Common manufacturer | |

| Performance | |

| Data width | 8 |

| Address width | 16 |

| Architecture and classification | |

| Instruction set | 6809 |

| Number of instructions | 59 |

| Physical specifications | |

| Transistors |

|

| Package |

|

The Motorola 6809 ("sixty-eight-oh-nine") is an 8-bit microprocessor with some 16-bit features. It was designed by Motorola's Terry Ritter and Joel Boney and introduced in 1978. Although source compatible with the earlier Motorola 6800, the 6809 offered significant improvements over it and 8-bit contemporaries like the MOS Technology 6502, including a hardware multiplication instruction, 16-bit arithmetic, system and user stack registers allowing re-entrant code, improved interrupts, position-independent code, and an orthogonal instruction set architecture with a comprehensive set of addressing modes.

The 6809 was among the most powerful (and most expensive) 8-bit processors of its era. In 1981 a 6809 in single-unit quantities was $37 compared to $9 for a Zilog Z80 and $6 for a 6502.[1] It was launched when a new generation of 16-bit processors were coming to market, like the Intel 8086, and 32-bit designs were on the horizon, including Motorola's own 68000. It was not feature competitive with newer designs and not price competitive with older ones.

Usage

[edit]The 6809 is used in the TRS-80 Color Computer, Dragon 32/64, SuperPET, ENER 1000, Fujitsu FM-7, the Cybernex LC3,[2] and Thomson MO/TO home computers, the Vectrex game console, and early 1980s arcade video games including Star Wars, Defender, Robotron: 2084, Joust, and Gyruss. 1990s Williams pinball machines are equipped with WPC-series controller boards based on 68B09.[3] Series II of the Fairlight CMI digital audio workstation and Konami's Time Pilot '84 arcade game each use dual 6809 processors.[4] Hitachi was a major user of the 6809 and later produced an updated version as the Hitachi 6309.

History

[edit]

6800 and 6502

[edit]The Motorola 6800 was designed beginning in 1971 and released in 1974. In overall design terms, it has a strong resemblance to other CPUs that were designed from the start as 8-bit designs, like the Intel 8080.[a] It was initially fabricated using early NMOS logic, which normally required several different power supply voltages. A key feature was an on-chip voltage doubler that allowed it to run on a single +5 V supply, a major advantage over its competitors like the Intel 8080 which required −5 V, +5 V, −12 V and ground.[5]

The 6800 was initially fabricated using the then-current contact lithography process. In this process, the photomask is placed in direct contact with the wafer, exposed, and then lifted off. There was a small chance that some of the etching material would be left on the wafer when it was lifted, causing future chips patterned with the mask to fail. For complex multi-patterned designs like a CPU, this led to about 90% of the chips failing when tested. To make a profit on the small number of chips that did work, the prices for the working models had to be fairly high, on the order of hundreds of dollars in small quantities.[6]

Some of the 6800's designers were convinced that a lower-cost system would be key to widespread acceptance. Notable among them was Chuck Peddle, who was sent on sales trips and saw prospective customers repeatedly reject the design as being too expensive for their intended uses. He began a project to produce a much less costly design, but Motorola's management proved uninterested and eventually told him to stop working on it. Peddle and some other members of the 6800 team left Motorola for MOS Technology and introduced this design in 1975 as the MOS Technology 6502.[7]

The 6800 was initially sold at $360 in single-unit quantities,[8] but had been lowered to $295. The 6502 was introduced at $25,[9] and Motorola immediately reduced the 6800 to $125. It remained uncompetitive and sales prospects dimmed. The introduction of the Micralign to Motorola's lines allowed further reductions and by 1981 the price of the then-current 6800P was slightly less than the equivalent 6502, at least in single-unit quantities.[1] By that point, however, the 6502 had sold tens of millions of units and the 6800 had been largely forgotten.

6809

[edit]While the 6502 began to take over the 6800's market, Intel was experiencing the same problem when the upstart Zilog Z80 began to steal sales from the Intel 8080. Both Motorola and Intel began new design cycles to leapfrog those designs. Intel responded by quickly introducing a small but practical upgrade of the 8080 as the 8085, which made it less expensive to use and more competitive with the Z80. They also began to design a series of 16-bit processors, which emerged as the Intel 8086 in 1978. Motorola also began the design of a similar high-end design, in the MACSS project,[10] but did not initially consider an improved 8-bit design. But when they polled their existing 6800 customers, they found that many were not willing to pay for a 16-bit design for their simple needs. This led to the decision to produce a greatly improved but compatible 8-bit design that became the 6809.[11]: 20, 26

Analysis of 6800 code demonstrated that loads and stores were the vast majority of all the time in CPU terms, accounting for 39% of all the operations in the code they examined. In contrast, mathematical operations were relatively rare, only 2.8% of the code. However, a careful examination of the loads and stores noted that many of these were being combined with adds and subtracts, revealing that a significant amount of those math operations were being performed on 16-bit values. This led to the decision to include basic 16-bit mathematics in the new design: load, store, add, and subtract. Similarly, increments and decrements accounted for only 6.1% of the code, but these almost always occurred within loops where each one was performed many times. This led to the addition of post-incrementing and pre-decrementing modes using the index registers.[11]: 26

The main goal for the new design was to support position-independent code. Motorola's market was mostly embedded systems and similar single-purpose systems, which often ran programs that were very similar to those on other platforms. Development for these systems often took the form of collecting a series of pre-rolled subroutines and combining them together. However, as assembly language is generally written starting at a base address, combining pre-written modules normally required a lengthy process of changing constants (or equates) that pointed to key locations in the code.[11]: 20, 24

Motorola's idea was to eliminate this task and make the building-block concept much more practical. System integrators would simply combine off-the-shelf code in ROMs to handle common tasks. Libraries of common routines like floating point arithmetic, graphics primitives, Lempel-Ziv compression, and so forth would be available to license, combine together along with custom code, and burn to ROM.[11]: 20, 24 [b]

In previous processor designs, including the 6800, there was a mix of ways to refer to memory locations. Some of these were relative to the current location in memory or to a value in an index register, while others were absolute, a 16-bit value that referred to a physical location in memory. The former style allows code to be moved because the address it references will move along with the code. The absolute locations do not; code that uses this style of addressing will have to be recompiled if it moves. To address this, the 6809 filled out its instruction opcodes so that there were more instances of relative addressing where possible.[12]: 1.2

As an example, the 6800 includes a direct addressing mode used to make code smaller and faster; instead of a memory address having 16-bits and thus requiring two bytes to store, direct addresses are only 8-bits long. The downside is that it can only refer to memory within a 256-byte window, the direct page, which is normally at the bottom of memory - the 6502 refers to this as zero page addressing. The 6809 added a new 8-bit DP register, for direct page. Code that formerly had to be in the zero page can now be moved anywhere in memory as long as the DP is changed to point to its new location.[12]: 1.2

Using DP solved the problem of referring to addresses within the code, but data is generally located some distance from the code, outside ROM. To solve the problem of easily referring to data while remaining position independent, the 6809 added a variety of new addressing modes. Among these was program-counter-relative addressing which allowed any memory location to be referred to by its location relative to the instruction. Additionally, the stack was more widely used, so that a program in ROM could set aside a block of memory in RAM, set the SP to be the base of the block, and then refer to data within it using relative values.[12]: 2.1–2.4

To aid this type of access, the 6809 renamed the SP to U for "user", and added a second stack pointer, S, for "system".[12]: 1.3 The idea was user programs would use U while the CPU itself would use S to store data during subroutine calls. This allowed system code to be easily called by changing S without affecting any other running program. For instance, a program calling a floating-point routine in ROM would place its data on the U stack and then call the routine, which could then perform the calculations using data on its own private stack pointed to by S, and then return, leaving the U stack untouched.[12]: 1.3

Another reason for the expanded stack access was to support reentrant code, code that can be called from various different programs concurrently without concern for coordination between them, or that can recursively call itself.[11]: 30 This makes the construction of operating systems much easier; the operating system had its own stack, and the processor could quickly switch between a user application and the operating system simply by changing which stack pointer it was using. This also makes servicing interrupts much easier for the same reason.[12]: 4 The 6809 adds a fast interrupt request (FIRQ) interrupt that saves only the program counter and condition code register before calling the interrupt code, whereas the IRQ interrupt saves all registers, taking additional cycles, then more to unwind the stack on exit.[12]: 1.9

The 6809 includes one of the earliest dedicated hardware multipliers.[11]: 36 It takes 8-bit numbers in the A and B accumulators and produces a result in A:B, known collectively as D.[12]: 1.1

Market acceptance

[edit]Much of the design had been based around the market concept of building-block code. But the market for pre-rolled ROM modules never materialized: Motorola's only released example was the MC6839 floating-point ROM. The industry as a whole solved the problem of integrating code modules from separate sources by using automatic relocating linkers and loaders, which is the solution used today.[13] However, the decisions made by the design team enabled multi-user, multitasking operating systems like OS-9 and UniFlex.

The added features of the 6809 were costly; the CPU had approximately 9,000 transistors compared to the 6800's 4,100 or the 6502's 3,500. While process improvements meant it could be fabricated cheaper than the original 6800, those same improvements were being applied to the other designs and so the relative cost remained the same. Such was the case in practice; in 1981 the 6809 sold in single-unit quantities for roughly six times the price of a 6502.[1] For those systems that needed some of its special features, like the hardware multiplier, the system could justify its price, but in most roles, it was overlooked.

Another factor in its low use was the presence of newer designs with significantly higher performance. Among these was the Intel 8086, released the same year, and its lower-cost version, the Intel 8088 of 1979. A feeling for the problem can be seen in the Byte Sieve assembly language results against other common designs from the era (taken from 1981[14] and 1983[15]):

| Processor | Seconds | Total clocks (millions) |

|---|---|---|

| 6502 1 MHz | 13.9 | 13.9 |

| Z80 4 MHz | 6.8 | 27.2 |

| 6809 2 MHz | 5.1 | 10.2 |

| 8086 8 MHz | 1.9 | 15.2 |

| 68000 8 MHz | 0.49 | 3.92 |

Although the 6809 did offer a performance improvement over the likes of the 6502[c] and Z80, the improvement was not in line with the increase in price. For those where price was not the primary concern, but outright performance was, the new designs outperformed it by as much as an order of magnitude.

Even before the 6809 was released, in 1976 Motorola had launched its own advanced CPU project, then known as Motorola Advanced Computer System on Silicon project, or MACSS. Although too late to be chosen for the IBM PC project, when MACSS appeared as the Motorola 68000 in 1979 it took any remaining interest in the 6809. Motorola soon announced that their future 8-bit systems would be powered by cut-down versions of the 68000 rather than further improved versions of the 6809.

Major uses

[edit]

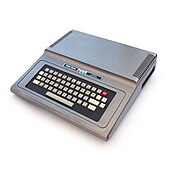

Its first major use was in the TRS-80 Color Computer, which happened largely by accident. Motorola had been asked to design a color-capable computer terminal for an online farm-aid project, a system known as "AgVision". Tandy (Radio Shack) was brought in as a retail partner and sold them under the name "VideoTex", but the project was ultimately canceled shortly after its introduction in 1980.[16] Tandy then re-worked the design to produce a home computer, which became one of the 6809's most notable design wins.[17]

Looking for a low-cost programming platform for computer science students, the University of Waterloo developed a system that combined a 6809-based computer-on-a-card with an existing Commodore PET, including a number of programming languages and program editors in ROM. The result was later picked up by Commodore, who sold it as the SuperPET, or MicroMainframe in Europe. These were relatively popular in the mid-1980s before the introduction of the PC clone market took over the programming role for most users.

Other popular home computer uses include the Fujitsu FM-7, Canon CX-1, Dragon 32/64, and the Thomson TO7 series. It was also available as an option on the Acorn System 2, 3 and 4 computers. Most SS-50 bus designs that had been built around the 6800 also had options for the 6809 or switched to it exclusively. Examples include machines from SWTPC, Gimix, Smoke Signal Broadcasting, etc. Motorola also build a series of EXORmacs and EXORset development systems.

Hitachi produced its own 6809-based machines, the MB-6890 and later the S1. These were primarily for the Japanese market, but some were exported to and sold in Australia, where the MB-6890 was dubbed the "Peach", probably in reference to the Apple II. The S1 was notable in that it contained paging hardware extending the 6809's native 64 kilobyte addressing range to a full 1 megabyte in 4 KB pages. It was similar in this to machines produced by SWTPC, Gimix, and several other suppliers. TSC produced a Unix-like operating system uniFlex which ran only on such machines. OS-9 Level II, also took advantage of such memory management facilities. Most other computers of the time with more than 64 KB of memory addressing were limited to bank switching where much if not all the 64 KB was simply swapped for another section of memory, although in the case of the 6809, Motorola offered their own MC6829 MMU design mapping 2 megabytes in 2 KB pages.[18]

The 6809 also saw use in various videogame systems. Notable among these, in the 68A09 incarnation, was the unique vector graphics-based Vectrex home videogame machine. It was also used in the Milton Bradley Expansion (MBX) system (an arcade console for the TI-99/4A home computer), and a series of arcade games released during the early to mid-1980s. Williams Electronics was a prolific user of the processor, which was deployed in Defender, Stargate, Joust, Robotron: 2084, Sinistar, and other games. The 6809 CPU forms the core of the successful Williams Pinball Controller. The KONAMI-1 is a modified 6809 used by Konami in Roc'n Rope, Gyruss, and The Simpsons.[19]

Series II of the Fairlight CMI (computer musical instrument) used dual 6809 CPUs running OS-9, and also used one 6809 CPU per voice card. The 6809 was often employed in music synthesizers from other manufacturers such as Oberheim (Xpander, Matrix 6/12/1000), PPG (Wave 2/2.2/2.3, Waveterm A), and Ensoniq (Mirage sampler, SDP-1, ESQ-1, SQ-80). The latter used the 6809E as their main CPU. The (E) version was used in order to synchronize the microprocessor's clock to the sound chip (Ensoniq 5503 DOC) in those machines; in the ESQ-1 and SQ-80 the 68B09E was used, requiring a dedicated arbiter logic in order to ensure 1 MHz bus timing when accessing the DOC chip.

In contrast to earlier Motorola products, the 6809 did not see widespread use in the microcontroller field. It was used in traffic signal controllers made in the 1980s by several different manufacturers,[20] as well as Motorola's SMARTNET and SMARTZONE Trunked Central Controllers (so dubbed the "6809 Controller"). These controllers were used as the central processors in many of Motorola's trunked two-way radio communications systems.[21]

The 6809 was used by Mitel as the main processor in its SX20 Office Telephone System.

Versions

[edit]The Motorola 6809 was originally produced in 1 MHz, 1.5 MHz (68A09) and 2 MHz (68B09) speed ratings. Faster versions were produced later by Hitachi. With little to improve, the 6809 marks the end of the evolution of Motorola's 8-bit processors; Motorola intended that future 8-bit products would be based on an 8-bit data bus version of the 68000 (the 68008). A microcontroller version with a slightly modified instruction set, the 6811, was discontinued as late as the second decade of the 21st century.

The Hitachi 6309 is an enhanced version of the 6809 with extra registers and additional instructions, including block move, additional multiply instructions, and division.

Legacy

[edit]Motorola spun off its microprocessor division in 2004. The division changed its name to Freescale and was subsequently acquired by NXP.

Neither Motorola nor Hitachi produce 6809 processors or derivatives anymore. 6809 cores are available in VHDL and can be programmed into an FPGA and used as an embedded processor with speed ratings up to 40 MHz.[citation needed] Some 6809 opcodes also live on in the Freescale embedded processors. In 2015, Freescale authorized Rochester Electronics to start manufacturing the MC6809 once again as a drop-in replacement and copy of the original NMOS device. Freescale supplied Rochester the original GDSII physical design database. At the end of 2016, Rochester's MC6809 (including the MC68A09, and MC68B09) is fully qualified and available in production.

Australian developer John Kent has synthesized the Motorola 6809 CPU in hardware description language (HDL).[22] This has made possible the use of the 6809 core at much higher clock speeds than were available with the original 6809. Gary Becker's CoCo3FPGA runs the Kent 6809 core at 25 MHz.[23] Roger Taylor's Matchbox CoCo runs at 7.16 MHz. Dave Philipsen's CoCoDEV runs at 25 MHz.[24]

Description

[edit]The 6809's internal design is closer to simpler, non-microcoded CPU designs. Like most 8-bit microprocessors, the 6809 implementation is a register-transfer level machine, using a central PLA to implement much of the instruction decoding as well as parts of the sequencing.

Like the 6800 and 6502, the 6809 uses a two-phase clock to gate the latches. This two-phase clock cycle is used as a full machine cycle in these processors. Simple instructions can execute in as little as two or three such cycles. The 6809 has an internal two-phase clock generator (needing only an external crystal) whereas the 6809E needs an external clock generator. There are variants such as the 68A09(E) and 68B09(E); the internal letter indicates the processor's rated clock speed.

The 6800, 6502, the 6809's clock system differs from other processors of the era. For instance, the Z80 uses a single external clock and the internal steps of the instruction process continue on each transition. This means that the external clock generally runs much faster; 680x designs generally ran at 1 or 2 MHz while the Z80 generally ran at 2 or 4. Internally, the 680x's divided the external clock frequency by four to create the system clock; so a 1 MHz 6809 would have a 4 MHz crystal or clock signal. Typically, on an instruction-for-instruction basis, they ran roughly twice as fast, when comparing the external clocks to other microprocessors.

The advantage to the 680x style access was that dynamic RAM chips of the era generally ran at 2 MHz. Due to the cycle timing, there were periods of the internal clock where the memory bus was guaranteed to be free. This allowed the computer designer to interleave access to memory between the CPU and an external device, say a direct memory access controller, or more commonly, a graphics chip. By running both chips at 1 MHz and stepping them one after the other, they could share access to the memory without any additional complexity or circuitry. Depending on version and speed grade, approximately 40–60% of a single clock cycle is typically available for memory access in a 6800, 6502, or 6809.

Registers and instructions

[edit]

The original 6800 included two 8-bit accumulators, A and B, a single 16-bit index register, X, a 16-bit program counter, PC, a 16-bit stack pointer, SP, and an 8-bit status register. The 6809 added a second index register, Y, a second stack pointer, U (while renaming the original S), and allowed the A and B registers to be treated as a single 16-bit accumulator, D. It also added another 8-bit register, DP, to set the base address of the direct page. These additions were invisible to 6800 code, and the 6809 was 100% source-compatible with earlier code.[12]: 1.1

Another significant addition was program-counter-relative addressing for all data manipulation instructions. This was a key addition for position-independent code, as it allows data to be referred to relative to the instruction, and as long as the resulting memory location exists then the instructions can be moved in memory freely. The system retained its previous addressing modes as well, although in the new assembler language, what were previously separate instructions were now considered to be different addressing modes on other instructions. This reduced the number of instructions from the 6800's 78 instructions to the 6809's 59. These new modes had the same opcodes as the previously separate instruction, so these changes were only visible to the programmer working on new code.[12]: 1.2

The instruction set and register complement are highly orthogonal, making the 6809 easier to program than contemporaries. Like the 6800, the 6809 includes an undocumented address bus test instruction which came to be nicknamed Halt and Catch Fire (HCF).[25][26]

Notes

[edit]- ^ In contrast to other early CPU designs that attempted to emulate minicomputer instruction sets and were much more complex.

- ^ Other examples are matrix arithmetic, Huffman encoding/decoding, statistical functions, string searching (e.g. by the Boyer-Moore algorithm) and tree structure management. A larger example is found in Motorola's 6809 programming manual, which contains the full listing of assist09, a so-called monitor, a miniature operating system intended to be burned in ROM.[12]: B.1

- ^ Which by this time was also widely available in 2 MHz versions, as used in the Atari 8-bit computers.

References

[edit]- ^ a b c Ancrona (1981).

- ^ "Cybernex XL display video terminal". York University Computer Museum Canada.

- ^ "Williams WPC - PinWiki". pinwiki.com. Archived from the original on 2022-07-30. Retrieved 2022-07-30.

- ^ "Konami Dual 6809 Based Hardware". System 16. Archived from the original on 2006-05-08. Retrieved 2020-04-23.

- ^ "8080A microprocessor - DIP 40 package". CPU World. Archived from the original on 2021-01-12. Retrieved 2021-01-30.

- ^ "Moore's Law Milestones". IEEE. 30 April 2015. Archived from the original on 24 February 2020. Retrieved 30 January 2021.

- ^ Peddle, Chuck (12 June 2014). "Oral History of Chuck Peddle" (Interview). Interviewed by Doug Fairbairn and Stephen Diamond. Archived from the original on 2021-12-11.

- ^ "Motorola microprocessor set is 1 MHz n-MOS". Control Engineering. 21 (11): 11. November 1974. MC6800 microprocessor price was $360. The MC6850 asynchronous communications interface adaptor (ACIA) was slated for first quarter 1975 introduction.

- ^ "MOS 6502 the second of a low cost high performance microprocessor family". Computer. 8 (9). IEEE Computer Society: 38–39. September 1975. doi:10.1109/C-M.1975.219074. Archived from the original on 2021-02-24. Retrieved 2021-01-30.

- ^ "Motorola 68000". The Vintage Technology Association. 17 May 2007. Archived from the original on 3 August 2020. Retrieved 2 February 2021.

{{cite web}}: CS1 maint: unfit URL (link) - ^ a b c d e f Ritter, Terry; Boney, Joel (January 1979). "The 6809, Part 1: Design Philosophy". BYTE. Vol. 4, no. 1. pp. 14–42.

- ^ a b c d e f g h i j k MC6809-MC6809E Microprocessor Programming Manual. Motorola. May 1983. Retrieved 13 May 2024.

- ^ Levine, John R. (2000) [October 1999]. "Chapter 1: Linking and Loading & Chapter 3: Object Files". Linkers and Loaders. The Morgan Kaufmann Series in Software Engineering and Programming (1 ed.). Morgan Kaufmann. ISBN 1-55860-496-0. Archived from the original on 2012-12-05. Retrieved 2021-06-22.

- ^ Gilbreath, Jim (September 1981). "A High-Level Language Benchmark". Byte. pp. 180–198.

- ^ Gilbreath, Jim; Gilbreath, Gary (January 1983). "Eratosthenes Revisited: Once More through the Sieve". BYTE. Vol. 8, no. 1. pp. 283–325.

- ^ "AgVision Videotex terminal". Vintage Computer. 2016-12-22. Archived from the original on 2018-04-17. Retrieved 16 April 2018.

- ^ G. Pitre, Boisy; Loguidice, Bill (2013). CoCo: The Colorful History of Tandy's Underdog Computer. Europe: CR Press. p. 19. ISBN 9781466592483. Archived from the original on 9 February 2023. Retrieved 16 February 2018.

- ^ "1981 Motorola Microprocessors Data Manual". 1981. Retrieved 2 April 2018.

- ^ Nicola Salmoria and the MAME Team. "konami: Portable Konami cpu emulator". Archived from the original on 2012-10-04. Retrieved 2012-10-21.

- ^ Robert J. Simpson; Raveendran Paramesran (1998). Advanced 8-bit Microprocessor, MC6809: Its Software, Hardware, Architecture & Interfacing Techniques. Springer. ISBN 978-981-3083-09-7.

- ^ "Motorola Type II SmartZone". The RadioReference Wiki. Archived from the original on 2021-02-06. Retrieved 2021-02-02.

- ^ "John Kent's Home Web Page". Archived from the original on 2001-05-10. Retrieved 2019-06-11.

- ^ "CoCo3FPGA - Davebiz Wiki". Archived from the original on 2020-09-15. Retrieved 2019-06-11.

- ^ "CoCoDEV - Davebiz Wiki". Archived from the original on 2020-09-15. Retrieved 2019-06-11.

- ^ David Banks. "Undocumented 6809 Behaviours". Archived from the original on 2023-01-22. Retrieved 2023-01-22.

- ^ John Bayko. "Great Microprocessors of the Present and the Past". Archived from the original on 2013-07-01. Retrieved 2013-07-01.

Bibliography

[edit]- "Ancrona is better" (PDF). Radio-Electronics (Advertising). Vol. 54, no. 4. April 1981. p. 111.

Further reading

[edit]- Datasheets and manuals

- MC6809 Datasheet; Motorola; 36 pages; 1983.

- MC6809E Datasheet; Motorola; 34 pages.

- Motorola 8-bit Microprocessors Data Book; Motorola; 1182 pages; 1981.

- Books

- 6809 Assembly Language Programming; 1st Ed; Lance Leventhal; 579 pages; 1981; ISBN 0-931988-35-7. (archive)

- The MC6809 Cookbook; 1st Ed; Carl Warren; 180 pages; 1980; ISBN 0-8306-9683-0. (archive)

- Advanced 8-bit Microprocessor: MC6809: Its Software, Hardware, Architecture and Interfacing Techniques; 1st Ed; Robert Simpson; 274 pages; 1998; ISBN 978-9813083097

- Programming the 6809; 1st Ed; Rodnay Zaks and William Labiak; 362 pages; 1982; ISBN 978-0895880789

- Magazines

- A Microprocessor for the Revolution: The 6809; Terry Ritter & Joel Boney (co-designers of 6809); BYTE magazine; Jan-Feb 1979. (archive) Archived 2010-02-15 at the Wayback Machine

- MC6809 microprocessor; Ian Powers; Microprocessors, Volume 2, Issue 3; July 1978; page 162; ISSN 0308-5953, doi:10.1016/0308-5953(78)90010-7.

- Reference cards

- MC6809 Reference Card; Motorola; 16 pages; 1981. (archive)

- 6809/6309 Reference Card; Chris Lomont; 10 pages; 2007. (archive)

External links

[edit]- Simulators / Emulators

- 6809 Emulation Page – collection of 6809 instructions, emulators, tools, debuggers, disassemblers, assemblers

- 6809 Emulator based on the SWTPC 6809 system

- Boards

- FPGA

- System09 6809 CPU core - VHDL source code - OpenCores - project website